Compaq Pro 2060u Manuel utilisateur

- Catégorie

- Surveille CRT

- Taper

- Manuel utilisateur

Ce manuel convient également à

SERVICE MANUAL

HIGH RESOLUTION DISPLAY MONITOR

Diamond Pro 2060u

NSZ2107STTUW

NEC-MITSUBISHI ELECTRIC VISUAL SYSTEMS CORPORATION

MARCH 2001

CBB-S5730

iii

Contents

1. Circuit description ...................................................................................................................... 1-1

1.1 Power block ......................................................................................................................... 1-1

1.1.1 Outline ...................................................................................................................... 1-1

1.1.2 Rectifying circuit ....................................................................................................... 1-1

1.1.3 Surge current suppression ...................................................................................... 1-1

1.1.4 Higher harmonic circuit ............................................................................................ 1-2

1.1.5 Sub power circuit ...................................................................................................... 1-4

1.1.6 Main power circuit..................................................................................................... 1-4

1.1.7 Degaussing circuit .................................................................................................... 1-7

1.1.8 Power management circuit ...................................................................................... 1-7

1.1.9 Protective circuit ....................................................................................................... 1-7

1.2 Horizontal deflection block ................................................................................................ 1-12

1.2.1 Distortion compensation waveform generating circuit ........................................ 1-13

1.2.2 Deflection current compensation circuit ................................................................ 1-22

1.3 Vertical output block ........................................................................................................... 1-24

1.4 High voltage block .............................................................................................................. 1-25

1.4.1 High voltage control circuit...................................................................................... 1-25

1.4.2 Protective function circuit ........................................................................................ 1-25

1.4.3 DBF (Dynamic Beam Focus) circuit ....................................................................... 1-27

1.5 CRT compensation block ................................................................................................... 1-29

1.5.1 Rotation circuit .......................................................................................................... 1-29

1.5.2 Corner purity circuit .................................................................................................. 1-29

1.5.3 Earth magnetism cancel circuit .............................................................................. 1-30

1.5.4 Digital dynamic convergence clear (DDCC) circuit ............................................. 1-31

1.6 Control block........................................................................................................................ 1-38

1.6.1 Sync. signal process ................................................................................................ 1-38

1.6.2 Front button ............................................................................................................... 1-38

1.6.3 I2C bus control .......................................................................................................... 1-38

1.6.4 Power control ............................................................................................................ 1-38

1.6.5 ABL, Beam protector ................................................................................................ 1-39

1.6.6 CRT support .............................................................................................................. 1-39

1.6.7 High voltage control ................................................................................................. 1-39

1.6.8 Display Data Channel .............................................................................................. 1-40

1.6.9 LED ............................................................................................................................. 1-40

1.6.10 Clamp pulse ............................................................................................................. 1-41

1.6.11 SPARK ...................................................................................................................... 1-41

1.6.12 Avoidance operation during input SYNC switching ........................................... 1-41

1.6.13 CS switch and vertical linearity switch ............................................................... 1-41

iv

1.6.14 H/W RESET ............................................................................................................. 1-41

1.6.15 Oscillation circuit..................................................................................................... 1-42

1.6.16 I/O expander ............................................................................................................ 1-42

1.7 Software ................................................................................................................................ 1-42

1.7.1 Outline ...................................................................................................................... 1-42

1.7.2 Frequency variation detection function ................................................................. 1-42

1.7.3 Memory of user timing ............................................................................................. 1-43

1.7.4 Picture adjustment .................................................................................................... 1-43

1.7.5 Power management.................................................................................................. 1-43

1.7.6 OSD display at NO SYNC ....................................................................................... 1-44

1.7.7 LED display................................................................................................................ 1-44

1.7.8 Status memory to EEPROM .................................................................................... 1-45

1.8 Deflection processor block ................................................................................................ 1-46

1.8.1 Outline ...................................................................................................................... 1-46

1.8.2 Vertical deflection waveform generating circuit ................................................... 1-46

1.8.3 Horizontal deflection drive waveform generating circuit..................................... 1-47

1.8.4 Distortion compensation waveform generating circuit ........................................ 1-47

1.8.5 DBF compensation waveform generating circuit ................................................. 1-47

1.8.6 Convergence compensation waveform generating circuit.................................. 1-48

1.8.7 Blanking waveform generating circuit.................................................................... 1-48

1.8.8 Moire canceling circuit ............................................................................................. 1-48

1.8.9 Distortion compensating operation ........................................................................ 1-50

1.9 Video block .......................................................................................................................... 1-51

1.9.1 Picture signal amplifier circuit ................................................................................ 1-51

1.9.2 Cut-off circuit ............................................................................................................. 1-51

1.9.3 2-input change over circuit and synchronizing signal circuit ............................. 1-54

1.9.4 On Screen Display circuit ........................................................................................ 1-56

1.9.5 AUTO SIZE function ................................................................................................. 1-57

1.10 USB circuit ......................................................................................................................... 1-59

1.10.1 Outline ...................................................................................................................... 1-59

1.10.2 USB downstream power supply............................................................................ 1-59

1.10.3 HUB controller power output................................................................................. 1-59

1.11 Wave form of main circuit voltage .................................................................................. 1-60

v

2. Adjustment procedure ............................................................................................................... 2-1

2.1 Measuring instruments ....................................................................................................... 2-1

2.2 Preparatory inspections ..................................................................................................... 2-1

2.3 Names of each monitor part .............................................................................................. 2-2

2.3.1 Configuration of front control panel ....................................................................... 2-2

2.3.2 Configuration of rear input connector.................................................................... 2-2

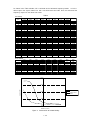

2.3.3 OSD display matrix ................................................................................................... 2-3

2.3.3.1 User mode ................................................................................................... 2-3

2.3.3.2 Factory mode .............................................................................................. 2-4

2.4 Adjustment ........................................................................................................................... 2-6

2.4.1 How to select the factory adjustment (FACTORY) mode ................................... 2-6

2.4.1.1 Selecting with front panel switches ......................................................... 2-6

2.4.2 Adjustments before aging........................................................................................ 2-6

2.4.2.1 Adjusting the high voltage and high voltage protector ......................... 2-6

2.4.2.2 SCREEN voltage / FOCUS adjustment ................................................... 2-7

2.4.2.3 Shock test .................................................................................................... 2-7

2.4.2.4 Preadjustment before aging...................................................................... 2-7

2.4.2.5 Adjusting the landing (ITC/4 corner purity adjustment)........................ 2-7

2.4.3 Adjustments after aging ........................................................................................... 2-7

2.4.3.1 +B adjustment ............................................................................................. 2-7

2.4.4 Adjusting the picture size, position and distortion (using automatic adjustment device) .. 2-8

2.4.4.1 Adjusting the picture inclination ............................................................... 2-8

2.4.4.2 Adjusting the back raster position ........................................................... 2-8

2.4.4.3 Adjusting the left/right distortion, picture width, picture position

(H-PHASE) and vertical linearity (all preset) ......................................... 2-8

2.4.4.4 Adjusting the DBF amplitude and phase ................................................ 2-9

2.4.5 Adjusting the cut off ................................................................................................. 2-10

2.4.6 Adjusting the RGB drive signal and X-Pro............................................................ 2-13

2.4.6.1 Adjusting the R, G, B drive signal (Adjustment of COLOR 1) ............. 2-13

2.4.6.2 Adjusting ABL.............................................................................................. 2-13

2.4.6.3 Adjustment of X-Pro (Timing No.A 30k / 70Hz Full white) ................... 2-14

2.4.6.4

Confirmation for operation of X-Pro

(Timing No.25 1800x1350 at 85Hz, Full white)

... 2-14

2.4.7 Adjusting the Purity .................................................................................................. 2-14

2.4.8 Adjusting the focus ................................................................................................... 2-15

2.4.9 Adjusting the convergence ...................................................................................... 2-16

2.4.9.1 Adjusting with ITC ...................................................................................... 2-16

2.4.9.2 Adjusting DDCP .......................................................................................... 2-18

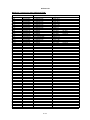

2.4.10 Default settings (With factory mode) ................................................................... 2-23

2.5 Inspections (In normal mode) ........................................................................................... 2-24

2.5.1Electrical performance .............................................................................................. 2-24

2.5.1.1 Withstand voltage ....................................................................................... 2-24

vi

2.5.1.2 Grounding conductivity check .................................................................. 2-24

2.5.1.3 Degaussing coil operation......................................................................... 2-24

2.5.1.4 POWER SAVE function operation

(Set the AC power input to 230V) ......

2-24

2.5.1.5 Confirming the CORNER-PURITY function ............................................ 2-25

2.5.1.6 Focus, picture performance

(Timing No.12 106.25kHZ / 85Hz 1600x1200)

.... 2-25

2.5.1.7 Misconvergence .......................................................................................... 2-25

2.5.1.8 Picture distortion ........................................................................................ 2-26

2.5.1.9 Linearity ..................................................................................................... 2-28

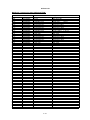

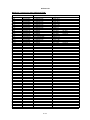

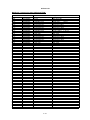

2.5.1.10 Adjustment value list................................................................................ 2-29

2.5.1.11 Confirming CLAMP PULSE POSITION, SYNC ON GREEN .............. 2-29

2.5.1.12 Checking the functions during Composite Sync input ........................ 2-30

2.5.1.13 Confirming the full white luminance ...................................................... 2-30

2.5.1.14 Confirming CONVERGENCE compensation function ......................... 2-30

2.5.1.15 Confirming ROTATION compensation function ................................... 2-30

2.5.1.16 Luminance/color coordination uniformity .............................................. 2-30

2.5.1.17 Confirming the full white color coordination ......................................... 2-30

2.5.1.18 Confirming the color tracking ................................................................. 2-31

2.5.1.19 CRT installation position ......................................................................... 2-31

2.5.1.20 Confirming FPM operation ...................................................................... 2-31

2.5.1.21 Confirming Auto size operation .............................................................. 2-31

2.5.1.22 Others......................................................................................................... 2-31

2.5.1.23 Confirming USB ........................................................................................ 2-31

2.6 DDC write data contents .................................................................................................... 2-32

2.7 Self-diagnosis shipment setting........................................................................................ 2-33

2.8 Default inspection ............................................................................................................... 2-33

2.8.1 Default setting of switches ...................................................................................... 2-33

2.8.2 Default setting of OSD ............................................................................................. 2-33

2.8.3 Checking the labels .................................................................................................. 2-33

2.8.4 Packaging .................................................................................................................. 2-33

2.9 Degaussing with handy-demagnetizer............................................................................. 2-34

2.9.1 General precautions ................................................................................................. 2-34

2.9.2 How to hold and use the handy-demagnetizer ................................................... 2-34

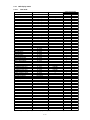

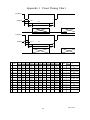

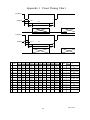

2.10 Timing chart ....................................................................................................................... 2-35

2.11 Adjustment timing ............................................................................................................. 2-36

3. Schematic diagram

4. Exploded view

<Appendix>

Specification

User's guide

All parts list

1 - 1

1. Circuit description

1.1 Power block

1.1.1 Outline

(1) The power block is compatible with 100 to 120VAC/220 to 240VAC(50/60Hz).

(2) The active filter circuit is adopted to suppress the higher harmonic current and improve

the power factor.

(3) The circuit that supplies the electric power to the secondary side is divided into two

circuits that are respectively called the main power and sub power.

Though both main and sub circuits supply the power to the secondary side in the normal

operation mode, the power is supplied from the sub power only in the power save mode

since the main power is stopped.

The main power is the configuration used the flyback converter type switching control IC of

the simulative resonant operation. Moreover, the sub power is the configuration used PRC

(OFF width fix) control IC.

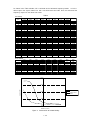

(4) The output on the secondary side is shown in Table 1.

(Refer to the power system diagram1-3 in Pages 1-3, 1-4 and 1-5.)

Table 1

1.1.2 Rectifying circuit

(1) The AC input voltage is rectified in the full wave mode with the diode bridge in D901.

(2) In the higher harmonic circuit of the section 1.1.4, the AC input current becomes the sine

wave form in the same phase with the AC input voltage waveform, but the interference is

given to other peripheral devices since the noise of the switching current appears on the

input side owing to the switching waveform. Therefore, L902 and C906 are inserted to

suppress the noise that is caused by the switching current.

1.1.3 Surge current suppression

(1) TH901 (thermistor) suppresses the rush current that flows when the power switch is turned

ON. Moreover, D933 is added to protect D902 from the rush current.

Power block

Main power

side

+215V

+80V

+15V

-15V

+12V

+7.5V

+5V

P-OFF+5V

H. deflection circuit, Video cut off circuit

Video circuit, DBF circuit, High voltage circuit

H/V deflection circuit, etc.

H/V deflection circuit, etc.

Video circuit, H. deflection circuit, etc.

Heater

MPU, etc.

Video circuit, etc.

Sub power

side

Output voltage

OFF

OFF

OFF

OFF

OFF

OFF

ON

OFF

When power save

Application

1 - 2

1.1.4 Higher harmonic circuit

(1) The pulsating waveform rectified in the full wave mode by D901 is switched throughout the full cycle

by the frequency of several tens kHz or more. Through this, the input current waveform becomes

an average of the switching currents of the partial cycles, thus becoming the sine waveform in the

macro. (See Fig.1)

(2) For the AC input voltage, the AC input current of the sine wave type in the same phase flows to

achieve the power circuit of improved power factor and reduced higher harmonic wave component.

(3) L903 is the choke coil, Q901 is MOS FET, D902 is the rectifying diode, C911 is the block capacitor,

and IC901 is the power factor improved controller. The power factor improved controller uses

MC33262P of Motorola. (See Fig. 2)

(4) After the sub power circuit operates, P-SUS signal becomes HI when +5V voltage is supplied to the

MPU. Then, Q902 is turned ON, the voltage of approx. +18V is supplied to pin8 (VCC terminal) of

IC901 through D929 from pin2 of T902, and the following operation is started.

(5) The pulsating voltage waveform rectified in the full wave mode by D901 is divided with R904, R905,

R906, R907 and R908 (100VAC : 1.1Vp-p and 240VAC: 2.9Vp-p), and is input to pin3 of IC901

(Multiplier input). Moreover, the output (+side of C911: 400VDC) of the higher harmonic circuit is

divided with R913, R914, R915, R916 and R917 (2.5VDC), and is input to pin1 of IC901 (error

amplifier input).

(6) The output of the error amplifier and the divided waveform of the pulsating voltage input to pin3 of

IC901 sets the threshold voltage of the current sense comparator to control the Q901 flowing

current from zero to the peak line of the AC input voltage in the sine wave pattern.

(7) When Q901 is turned ON, the drain current of Q901 flows to R910 and R937 to drop the voltage,

and the voltage generated by the voltage drop is input to pin4 (current sense input) of IC901. When

the voltage reaches the threshold voltage of the current sense comparator, Q901 is turned OFF.

(8) When Q901 is turned OFF, the accumulated energy of L903 starts to be supplied to the load

through D902.

(9) As the accumulated energy of L903 drops, the auxiliary coil voltage (pin8 of L903) also drops.

When it reaches the threshold voltage of *zero current detector, Q901 will be turned ON again.

* Pin 5 of IC901 is the zero current detection terminal to input the auxiliary coil voltage of pin10 of

L903. The zero current detector monitors that the auxiliary coil voltage drops beyond the thresh

old voltage. Thus, the accumulated energy of L903 is indirectly detected.

(10) The above operation is repeated to continue the oscillating operation. Thus, the DC voltage (L903,

Q901, D902 and C911 compose the voltage rise circuit.) is gained on the output, and the AC input

current of the sine wave in the same phase with the AC input voltage is gained on the input side.

Figure 1. L903 coil current

1 - 3

Figure 2. High harmonic waveform circuit

1 - 4

1.1.5 Sub power circuit

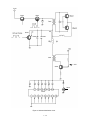

(1) The sub power uses PRC control regulator STR-G6352 (IC903) produced by Sanken Electric. (See Fig.3)

(2) When the power switch is turned ON, the rectified and smoothened DC voltage (AC voltage

x ) is supplied to pin4 of IC903, through R950, R951 and R952. When pin4 reaches

approx. 17V, the built-in output FET is put into operation. (Since Q902 is OFF, IC902 and

IC 903 do not operate.)

(3) This also induces the voltage at pin2 of T902 and on the secondary side. These outputs

are respectively rectified, and are used as the power for control on the primary side and

the power for the MPU.

(4) IC903 monitors +5V and -15V output on the secondary side by IC922 (Shunt regulator),

and suppresses the voltage regulation by feeding back to pin 5 of IC903 via IC912

(Photocoupler).

(5) When the voltage on the secondary side starts, the MPU will be put into operation and the

P-SUS signal line will become HIGH.

(6) This information is transmitted to the primary side via IC913 to turn ON Q902.

When Q902 is turned ON, the power for control on the primary side will be supplied to

IC901 and IC902 to operate the higher harmonic circuit. Thus, the main power circuit will

be put into operation.

1.1.6 Main power circuit

(1) The main power circuit adopts the flyback type switching power of pseudo-reosonance

operation. This is composed of a Sanken brand hybrid IC STR-F6676 (IC902) that inte-

grates the power MOS-FET and control IC.

The circuit operation is described as follows. (See Fig. 4.)

(2) The timing at that the power MOS-FET is turned ON is consistent with the bottom point of

the voltage resonant waveform after the transformer (T901) discharges the energy to the

secondary side, that is, a half cycle of the resonant frequency determined by LP value

(primary coil inductor value) of T901, and C914 (resonant capacitor). This is called

pseudo-reosonance operation. The advantage of such an effect is that the switching loss

is reduced by turning it ON when the voltage between the drain sources of the power MOS-

FET becomes the lowest.

(3) Like the higher harmonic circuit, voltage of approx. +18V is supplied to the Vcc terminal

(Pin 4) of IC902 (STR-F6676) via D929 from pin2 of T902 when Q902 is turned ON by the

P-SUS signal from the MPU.

When the voltage of Pin 4 of IC902 reaches 16V, the control circuit will be put into opera-

tion to turn ON the integrated MOS-FET.

(4) When MOS-FET is turned ON, the capacitor C1 in IC will be charged to approx. 6.5V. On

the other hand, the drain current flows to R928, and the voltage generated by the voltage

drop is applied to pin1 (OCP/FB terminal) of IC902.

When the voltage of Pin 1 reaches approx. 0.73V, the comparator (Comp. 1) in IC will be

activated to turn OFF MOS-FET.

(5) The voltage between both ends of C1 drops to approx. 3.7V. the oscillator output will be

reversed again to turn ON MOS-FET.

The above is repeated to continue the oscillation operation.

(6) Here, IC902 monitors +215V of the output on the secondary side with IC921 (error ampli-

fier) and feeds back it to pin1 of IC902 via IC911 (photocoupler), thus suppressing the

voltage fluctuation of the primary side.

1 - 5

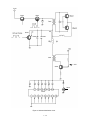

Figure 3. IC903 (STR-G6352) block diagram and peripheral circuit

4

3

1

6

7

8

5

T902

R935

R950

(AC x 2 )V

R951

R952

Vin

4

D932

C931

C940

Icont

S Q

R

OSC

REG

Latch Delay

Drive

OVP

Vth=25.5V

Vth=0.73V

Vth=1.45V

Ta=160°C

TSD

Tr i

REG1

PQM Latch

UVLO

Internal Bias

Toff=15µS

IC903 (STR-G6352)

Vin(on)=17.5V

Vin (off)=10V

OCP Comp.

D

GND

D971

L971

C972

C971

R931

R936C933

C939

D941

R939

++

+

-

+

-

+

-

+

-

+

-

2

1

2

5

3

1 - 6

Figure 4. IC902 (STR-F6676) block diagram and peripheral circuit

C912

D904

R928

C916

C914

C917

Iconst

START

LATCH

DRIVE

REG.

T. S.D

Waveform5

(Refer to P1-11)

5

4

3

4

3

2

9

7

T901

400V

D912

R927

2

1

-

+

Vth(1)

-

+

Vth(2)

Comp.1

Comp.2

Rconst -Rconst +

R2

R926

C1 R1

R3

R4

O.S.C

O.V.P

5

D908

R922

R923

R941

R925

IC902(STR-F6676)

1 - 7

1.1.7 Degaussing circuit

(1) The automatic and manual degaussing circuit is provided.

The circuit prevents the picture from dropping its quality due to the magnetization on CRT,

and operates as follows.

(2) When powering ON, Q963 flows to activate RY901 by DG signal output by the MPU.

This will make the current flow through the demagnetizing coil for demagnetization. The

demagnetizing time is approximately 5 seconds.

Manual demagnetization becomes possible by selecting the demagnetizing menu on the

OSD picture.

1.1.8 Power management circuit

Turn ON the power management setting on the menu picture of OSD, and the energy saving

mode shown in Table 2 will be ready depending on whether the horizontal/vertical sync. signal

is present or not.

1.1.9 Protective circuit

(1) Overcurrent protective circuit (primary side)

IC902 is provided with an overcurrent protective circuit. The voltage drop generated by the

drain current that flows into R928 is input to Pin 1 (OCP/FB terminal) of IC902. When the

voltage reaches 0.73V, the overcurrent protective circuit will be activated.

(2) Overcurrent protective circuit (secondary side)

To protect the parts on the secondary side, the short-circuit detection circuit is provided on

the secondary side output (+215V, +80V, +/-15V, +7.5V), one for each. As an example of

+215V, the output line of +215V is monitored with R964, R965, D966 and Q961. If it drops

beyond approx. +140V for any reason, Q961 will be turned ON to transmit the information

to the MPU. Then, since the MPU sets P-SUS signal at LOW, Q902 will be turned OFF to

cut off the power to IC902 in order to stop IC902. (IC901 will be also stopped at the same

time.) The overcurrent protective circuit is designed to be activated when the output volt-

age drops approx. 30 to 40%.

(3) Overvoltage protective circuit

R918, R919, R920 and R921 are used to detect the overvoltage in the higher harmonic

circuit, and the tertiary coil (Pin 9) of T901 is used to detect the overvoltage of the voltage

on the secondary side. They are both connected to the overvoltage protective circuit

(Q904, Q905) on the primary side. If any overvoltage results for any reason, Q905 will be

turned ON to turn ON Q904. Then Q902 will be stopped. Since the power for IC901 and

IC902 is cut off as Q902 is stopped, the switching operation will be stopped.

OFF

ON

On

Off

On

Off

On

On

Off

Off

Active

Blank

Blank

Blank

Power Save Video

H-sync V-sync

LED indicator

140W

3W

Power

consumption

Recovery

time

5 sec.

Green

Amber

1 - 8

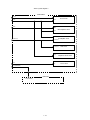

+215V

+80V

+15V

-15V

P_OFF+5V

+5V

+7.5V(HEATER)

+215V

+80V

+15V

+12V

-15V

P_OFF+5V

+5V

+5V

+215V

+80V

+12V

+5V

P_OFF+5V

+7.5V(HEATER)

PWB-POWER

PWB-MAIN

PWB-VIDEO

+5V

-15V

+3.3V

PWB-DEFL-SUB

P_OFF+5V

-15V

~ Power system diagram 1 ~

1 - 9

PWB-MAIN

Horizotnal width/PCC

control circuit

+B

+15V

-15V

+12V

Horizontal drive circuit

-15V

MPU circuit

+5V

Vertical system circuit

+15V

-15V

DBF circuit

+80V

+12V

-15V

High voltage system circuit

+80V

+12V

Corner purity

H/V ROTATION

Drive circuit

+15V

-15V

P-OFF+5V

+80V

P-OFF+5V

-15V

+5V

Variable

circuit

(Chopper circuit)

+215V

+B

+15V

+12V

PWB-DEFL-SUB

Reg.

3.3VP_OFF+5V

P_OFF+5V -15V

~ Power system diagram 2 ~

1 - 10

PWB-VIDEO

Cut off circuit

+215V

+12V

Main amplifier circuit

+80V

+12V

OSD circuit

P-OFF+5V

Magnetic cancel circuit

+12V

Asset circuit

+5V

Preamplifier circuit

+12V

P-OFF+5V

+215V

+12V

P-OFF+5V

+80V

+5V

+7.5V(HEATER)

+7.5V(HEATER)

PWB-CRT

~ Power system diagram 3 ~

1 - 11

Waveform 1. Top :AC input voltage

Bottom :AC input current

Waveform 2. Top :Q901 drain voltage

Bottom :Q901 drain current

Waveform 3. Top :Q901 drain voltage

Bottom :Q901 drain current

Waveform 4. Top :IC903 drain voltage

Bottom :IC903 drain current

Waveform 5. Top :IC902 drain voltage

Bottom :IC902 drain current

1 - 12

1.2 Horizontal deflection block

The operating principle of the horizontal deflection circuit is given below.

The Q502 operates as horizontal output, and the D503 as the dumper diode.

As shown in Fig. 5, the horizontal output transistor Q502 turns to ON/OFF by means of the drive pulse in

pin 25 of IC601 in substrate DEFL-SUB through the drive transformer T501, drive transistor Q501, or

Q560, Q561, Q562, etc.

The deflection current Idy during Q502 ON gets increased to the maximum level Ip according to the

equation shown below:

Idy = (Vcc/Ldy) x Ton

The maximum Ip is approximately 8A at full scan when fh = 106k.

Here;

Vcc: Output voltage of Q504

Ldy: Parallel value of the Lh value of DY (=62µH) and the horizontal output transformer

(=5mH)

TON: The ON time of Q502

When the drive pulse has negative polarity, Q502 turns OFF and Idy starts flowing to charge C506 until

the collector voltage reaches the maximum level Vcp.

Vcp = Vccx{1 + (π/2)x(Ts/Tr)}

With the maximum Vcp attained, the charges accumulated in C506 flow into DY as the discharge current.

This charge/discharge current is called retrace time, and is expressed by the equation given below.

Tr = π (Ldy•Cr) * Cr = C506 value

In the present model, the retrace time is set to approx. 1.8µs.

Ts is called trace time, and is expressed by the equation given below with the horizontal cycle as T.

T = Ts + Tr

With Vcp = 0, the dumper diode D503 turns ON and Idy gets decreased from –Ip to 0 ampere. Since

Q502 ON time and dumper diode ON time are set to overlap at 0 ampere point of Idy, the crossover

distortion is prevented from occurring at 0 ampere point of Idy.

The D503 causes the transient current to flow in the high-speed dumper diode.

The horizontal output transformer T502, connected in parallel to the deflection yoke, operates as a choke

coil. Figs. 6 and 7 show the image of circuit operation and the waveforms in actual machine.

1 - 13

1.2.1 Distortion compensation waveform generating circuit

The deflection distortion compensation waveform for horizontal size system is output from pin

64 of IC601. This waveform is output from 1-bit DAC, with 3.3V pulse waveform with resolu-

tion 25MHz output at pin 64. This pulse waveform is leveled by the low-pass filters R632 and

C622 to obtain the vertical cycle compensation waveform, with the amplitude 1.0 to 1.2Vp-p

and connected to pin5 of IC5J1.

The compensation waveform circuit carries out horizontal size and trapezoid compensation,

side pin compensation, side pin top and bottom compensation, side pin S-shape compensation

and side pin W compensation. (Refer to Compensation Image Diagram in Fig. 22)

The deflection compensation waveform for horizontal phase system is output from pin 57 of

IC601. The pin 57 has 1-bit DAC output and outputs the 3.3V pulse waveform with 25MHz

resolution. This pulse waveform is then leveled by the low-pass filters R619, R614, C604 and

C601 to obtain the vertical cycle waveform, which is then electrically added to the horizontal

system PLL filter (pin 20 of IC601) to carry out the deflection distortion compensation of the

horizontal phase system. It carries out parallelogram distortion compensation and side pin

balance (top and bottom) correction. (Refer to the Compensation Image Diagram in Fig. 22.)

The control of horizontal screen width and the side PCC control are carried out by IC5J1, Q503

and Q504. First, the horizontal width signal and each distortion compensation signal im-

pressed in pin 5 of IC5J1 from pin 64 of IC601 are compared with the AFC pulse signal recti-

fied and fed back to pin 13 of IC5J1. The signals are further compared with the constant-

inclination type saw-tooth wave synchronized with the horizontal cycle created inside IC before

turning into the PWM signal of square wave. This PWM signal output from pin 9 of IC5J1

carries out the above control by driving the Q504 gate. Fig. 8 shows the block diagram of

IC5J1 and Fig. 9 the operation image waveforms.

IC5K1 connected to pin 8 of IC5J1 is a transistor with 2 circuits.

Pins 1 and 3 of IC5K1 are for the base, pin 2 is for GND and pins 4 and 5 are for the collector.

Pin 32 of IC101 connected to pin 3 makes pins 5 and 2 open/short by P-SUS signal.

When P-SUS signal is LOW, pin 8 of IC5J1 is led into GND from pin 5 of IC5K1, and make

SYNC input of IC5J1 LOW. As IC5J1 stops operation without SYNC input, Q504 turns OFF

and horizontal deflecting output stops.

Due to this process, destruction by wrong pulse is prevented when it exceeds in Q502.

The Q503 works as a ripple filter in 215V line and keeps the Q503 emitter voltage constant

even if there is a slight fluctuation in the collector voltage of Q503. The Q503 collector has

215V applied to it, with the emitter output being stable at 203V. This is mainly effective in

dynamic regulation.

The horizontal raster position is adjusted by using Q5A1, Q5A2, VR5A1 and T502. The refer-

ence voltage is obtained from the connecting point of Cs and is then input into pin 2 of T502.

When the emitter voltage in Q5A1 and Q5A2 has the DC level increased by adjusting VR5A1,

the current flows to DY side, causing the raster to move left. Reversely, when the DC level of

the emitter voltage is decreased, the current flows to Q5A2 side, causing the raster to move

right.

The Idy DC level is adjusted by varying the emitter voltage of Q5A1 and Q5A2 at the timing

No. 25 (120kHz/85Hz) using VR5A1, so that the raster position comes at the center of CRT.

The operation image is shown in Fig. 10.

This adjustment, however, is confined to the factory, and is not open to the users.

1 - 14

Figure 5 Horizontal deflection circuit

Q503 Q504

T502

Q502

D503 C506

L540

LIN

IC501

Q540

Q510

215V

1 - 15

Figure 6 Horizontal deflection circuit operation image

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

La page charge ...

-

1

1

-

2

2

-

3

3

-

4

4

-

5

5

-

6

6

-

7

7

-

8

8

-

9

9

-

10

10

-

11

11

-

12

12

-

13

13

-

14

14

-

15

15

-

16

16

-

17

17

-

18

18

-

19

19

-

20

20

-

21

21

-

22

22

-

23

23

-

24

24

-

25

25

-

26

26

-

27

27

-

28

28

-

29

29

-

30

30

-

31

31

-

32

32

-

33

33

-

34

34

-

35

35

-

36

36

-

37

37

-

38

38

-

39

39

-

40

40

-

41

41

-

42

42

-

43

43

-

44

44

-

45

45

-

46

46

-

47

47

-

48

48

-

49

49

-

50

50

-

51

51

-

52

52

-

53

53

-

54

54

-

55

55

-

56

56

-

57

57

-

58

58

-

59

59

-

60

60

-

61

61

-

62

62

-

63

63

-

64

64

-

65

65

-

66

66

-

67

67

-

68

68

-

69

69

-

70

70

-

71

71

-

72

72

-

73

73

-

74

74

-

75

75

-

76

76

-

77

77

-

78

78

-

79

79

-

80

80

-

81

81

-

82

82

-

83

83

-

84

84

-

85

85

-

86

86

-

87

87

-

88

88

-

89

89

-

90

90

-

91

91

-

92

92

-

93

93

-

94

94

-

95

95

-

96

96

-

97

97

-

98

98

-

99

99

-

100

100

-

101

101

-

102

102

-

103

103

-

104

104

-

105

105

-

106

106

-

107

107

-

108

108

-

109

109

-

110

110

-

111

111

-

112

112

-

113

113

-

114

114

-

115

115

-

116

116

-

117

117

-

118

118

-

119

119

-

120

120

-

121

121

-

122

122

-

123

123

-

124

124

-

125

125

-

126

126

-

127

127

-

128

128

-

129

129

-

130

130

-

131

131

-

132

132

-

133

133

-

134

134

-

135

135

-

136

136

-

137

137

-

138

138

-

139

139

-

140

140

-

141

141

-

142

142

-

143

143

-

144

144

-

145

145

-

146

146

-

147

147

-

148

148

-

149

149

-

150

150

-

151

151

-

152

152

-

153

153

-

154

154

-

155

155

-

156

156

-

157

157

-

158

158

-

159

159

-

160

160

-

161

161

-

162

162

-

163

163

-

164

164

-

165

165

-

166

166

-

167

167

-

168

168

-

169

169

-

170

170

-

171

171

-

172

172

-

173

173

-

174

174

-

175

175

-

176

176

-

177

177

-

178

178

-

179

179

-

180

180

-

181

181

-

182

182

-

183

183

-

184

184

-

185

185

-

186

186

-

187

187

-

188

188

-

189

189

-

190

190

-

191

191

-

192

192

-

193

193

-

194

194

-

195

195

-

196

196

-

197

197

-

198

198

-

199

199

-

200

200

-

201

201

-

202

202

-

203

203

-

204

204

-

205

205

-

206

206

-

207

207

-

208

208

-

209

209

-

210

210

Compaq Pro 2060u Manuel utilisateur

- Catégorie

- Surveille CRT

- Taper

- Manuel utilisateur

- Ce manuel convient également à

dans d''autres langues

- English: Compaq Pro 2060u User manual

Autres documents

-

NEC 2060u Manuel utilisateur

-

NEC Diamond Pro 740SB Le manuel du propriétaire

-

Dell Rack Console 17FP Manuel utilisateur

-

NEC DiamondPlus 200 Le manuel du propriétaire

-

Daewoo 103FH Manuel utilisateur

-

NEC Diamond Pro 920 Le manuel du propriétaire

-

NEC Diamond Pro 2040U Le manuel du propriétaire

-

NEC Diamond Pro 730 Le manuel du propriétaire

-

Sony XM SD22X Manuel utilisateur

-

RGBlink CP2048 Guide de démarrage rapide